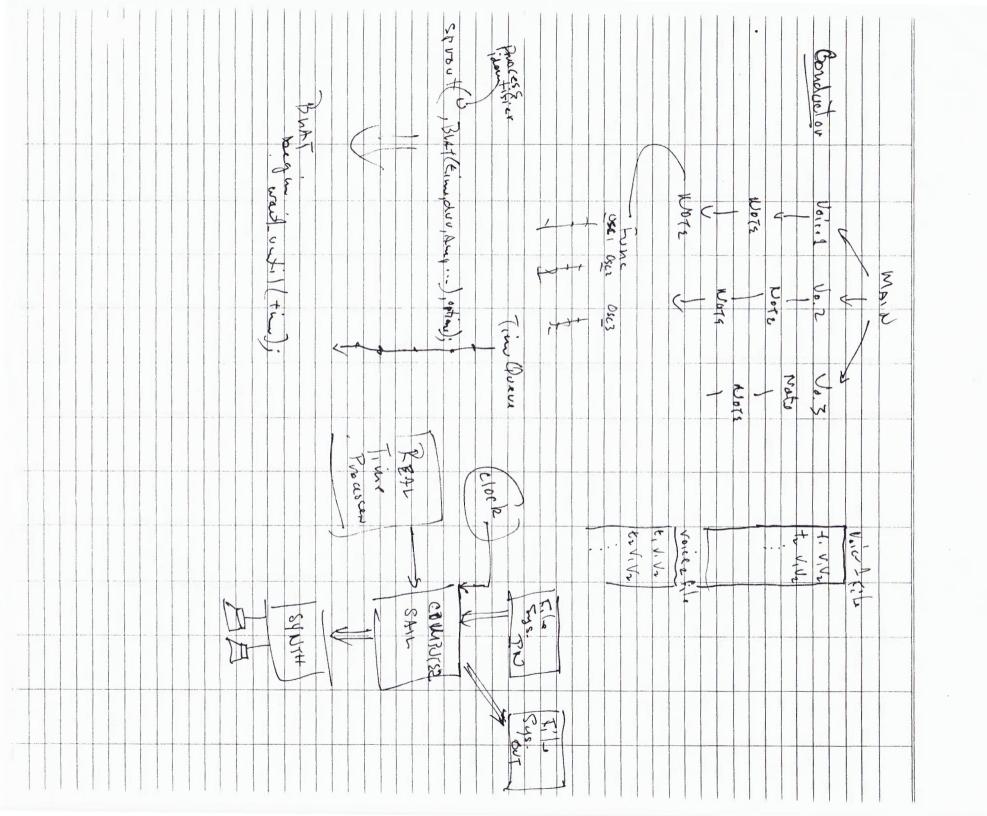

## Generators and Modifiers

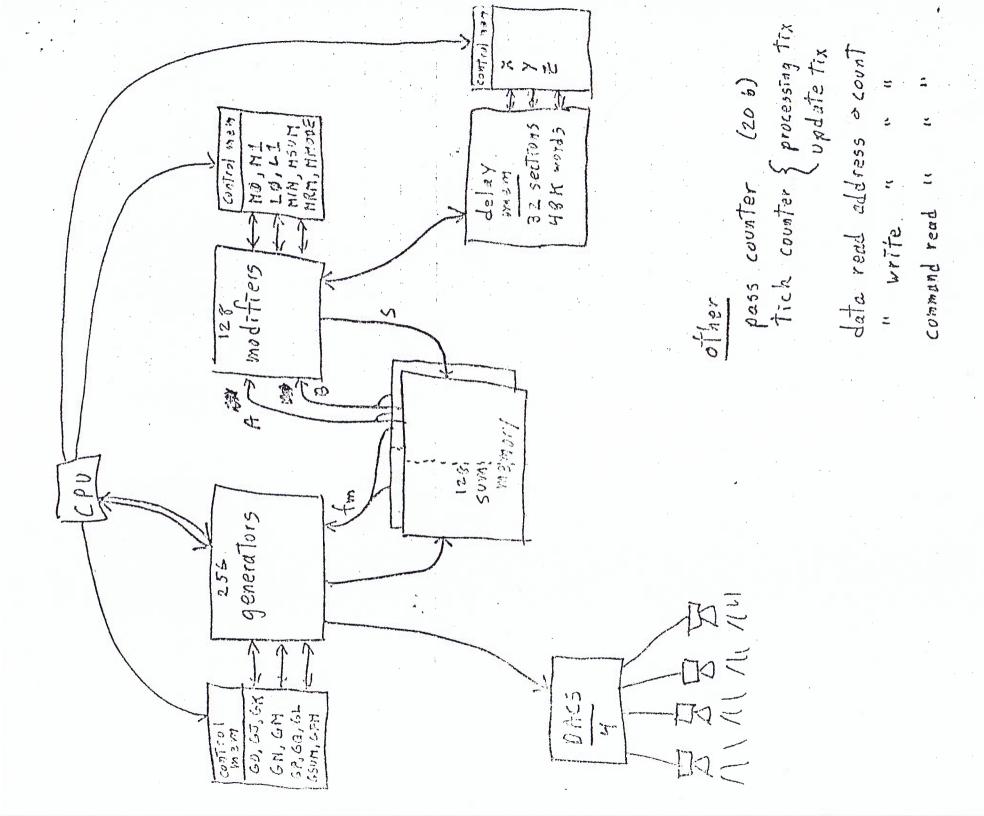

The synthesizer has two kinds of processing elements: generators and modifiers. An additional type of element, termed a delay unit, is optional.

Generators produce sine, square, and sawtooth waves, pulse trains, equal-amplitude sum-of-cosines (band-limited pulse trains); apply linear and exponential envelopes; perform frequency modulation; can automatically sweep frequency linearly; read data from computer memory; and write data into computer memory or digital-to-analog converters. Up to 256 generators can be active at one time.

Modifiers simulate a resonance or antiresonance; perform amplitude modulation, four-quadrant multiplication, mixing, clipping, and memory (sample and hold) functions; can generate uniform noise; and pass data to and from the optional delay units. Up to 128 modifiers can be active at the same time.

Delay units have two uses: as delay lines for signals; and to hold precomputed tables, such as time-domain waveforms. Up to 32 delay units can be active at the same time.

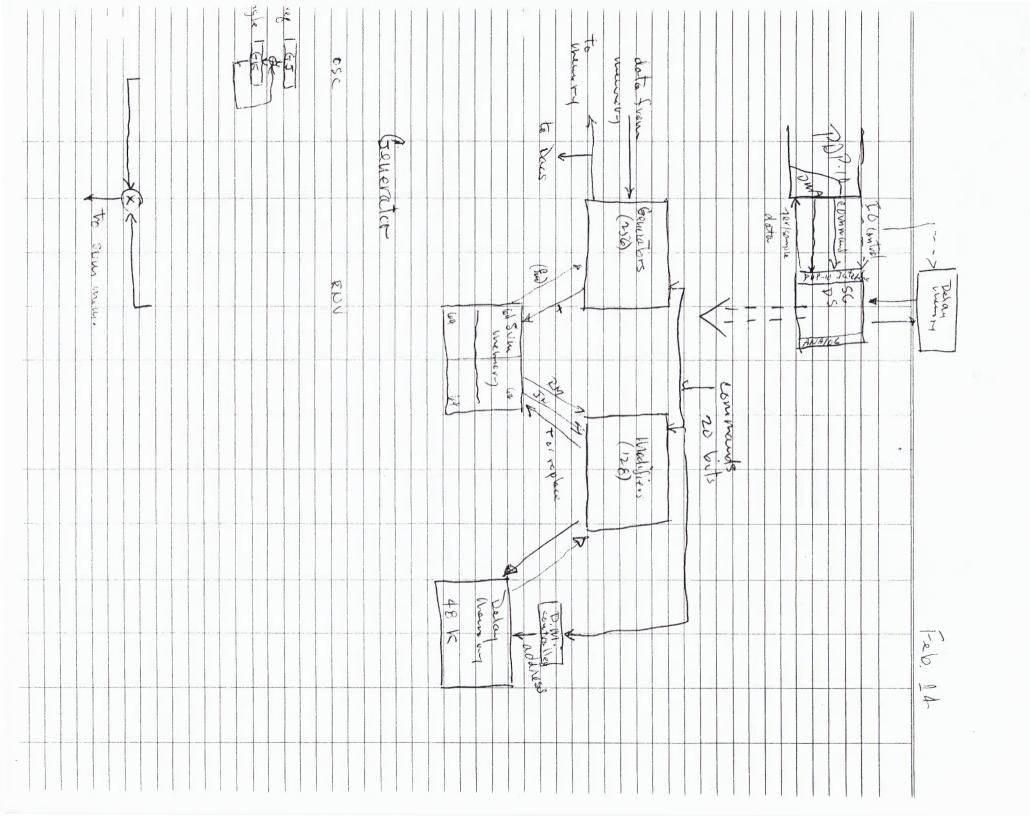

## Passes and Ticks; Sum Memory

The processing performed on a per-sample basis comprises one pass. A pass is a series of ticks; of two types: processing ticks and update ticks. Processing ticks perform the calculations corresponding to generators and modifiers, and update ticks permit loading of new parameters. Within a pass, all processing ticks are performed first, then all update ticks. A tick of either type takes 195 nsec. The number of processing ticks is nine more than the maximum of: the number of generators used; twice the number of modifiers used. For delay units, divide the number of processing ticks minus six by four to get the number of delay memory cycles possible per pass. The number of delay units that can be used is this number less however many delay memory cycles the computer may make during the processing ticks. The number of update ticks should be chosen according to the number of processing ticks to give the desired overall sample rate.

Information is passed among generators and modifiers through a scratchpad area called sum memory, which is divided into four 64-word quadrants. In one quadrant, sums are accumulated of generator outputs during a given pass; another quadrant holds the accumulated generator sums from the previous pass. The other two quadrants act likewise for modifier outputs. Any generator or modifier can read data from either previous-pass quadrant, and any modifier can read from the current-pass modifier quadrant also.

70416

42/2 1500 (full Velson)

MOIDY!

Pont use bat

keep - DGL

## Computer Interface

Information is passed to and from the computer in two ways: I/O instructions, and direct memory access. With the delay memory option, a low-bandwidth bidirectional 20-bit path permits read- and write-accesses by the computer.

Computer I/O instructions perform general control, status sensing, and diagnostic functions. The direct memory access path is provided for data transfer in real time. There are three types of such data transfer: commands (to the device), read data (one datum per sample) (to the device), and write data (one datum per sample) (from the device). Each of these three has its own word count (WC) and core address (CA) registers in the device; they are set up by I/O instructions. Commands are always 32 bits; read data and write data may each be either 16 or 32 bits, giving a choice between packed data and full precision (the left 20 bits are significant in 32-bit mode; in 16-bit mode, the left 16-bit sample precedes the right one). The device has buffering for 28 commands, 4 read-data items, and 1 write-data item.

The synthesizer can be conditioned to interrupt the computer in various circumstances. One class of them can be termed data errors: arithmetic overflow during processing, and command overrun (more updates specified to be performed on a pass than update ticks provided). The other class of interrupt conditions relates to direct memory access. Separate indications are provided for read data, write data, and command WCs being exhausted, and also for underrun conditions. Command underrun occurs when on an update tick there is no command to be performed (normally when there is no update activity due, a Linger command is being performed). The read data and write data underrun conditions occur when the device must stop its clock momentarily to wait for memory access; this means the device is not operating in real time.

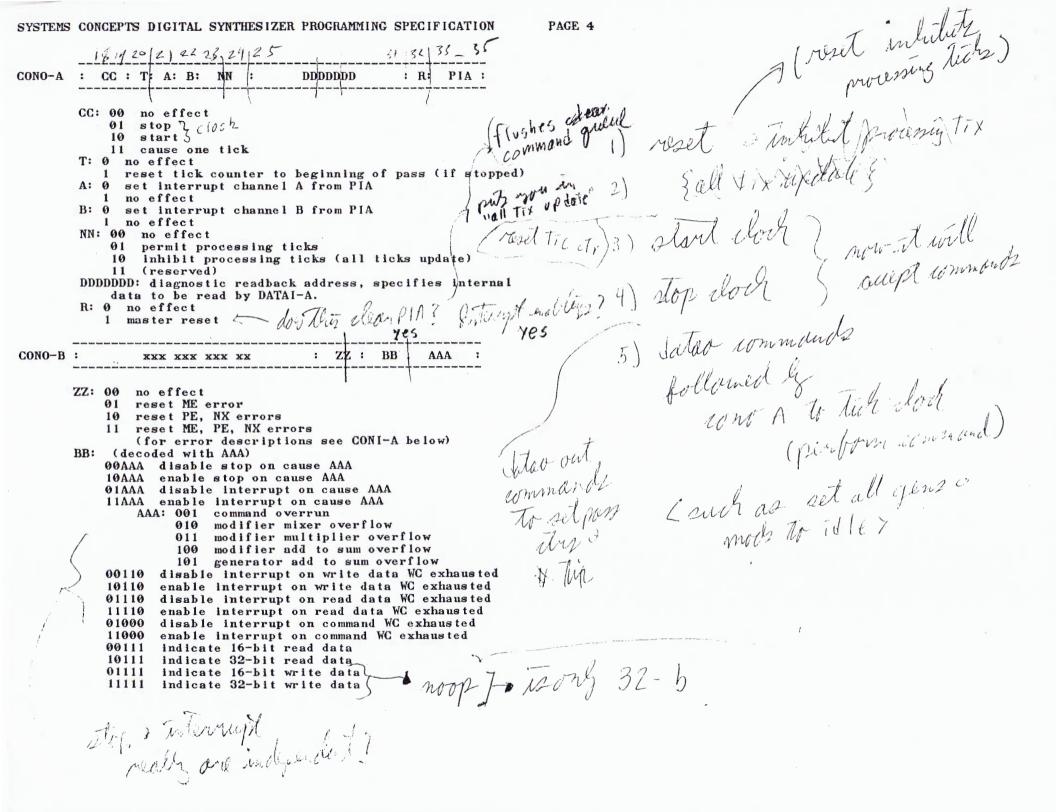

#### PDP-10 INTERFACE

The computer interface specifications are discussed here in terms of the implementation for the PDP-10 computer. Direct memory access refers to 32-bit data and commands right-justified in 36-bit words. The synthesizer uses a group of four contiguous device codes (beginning with one which is divisible by four), referred to below as A, B, C, and D. Codes A, B, and C are used by the basic synthesizer; code D is used for the Delay Memory option. Two priority interrupt channels are employed; channel B for command word count exhausted, and channel A for all other interrupt causes.

## Summary

```

CONO-A 18 bits: sets overall status, diagnostic readback address

CONO-B 18 bits: sets miscellaneous status

DATAO-A 32 bits: (only when not running) performs command

DATAO-B 32 bits: sets CA (core address) or WC (word count) for

commands, read data, write data

DATAO-C 20 bits: (only when not running) for diagnostic purposes,

sets write-buffer data from bits 4-23

DATAO-D 36 bits: writes bits 0-19 into Delay Memory location

designated by bits 20-35. Data overwritten

is saved to be read by DATAI-D.

CONI-A (18) bits: reads overall conditions

CONI-B 18 bits: reads cause of interrupt

DATAL-A 20 bits: (only when not running) diagnostic readback

DATAI-D 20 bits: reads Delay Memory data saved when overwritten by

most recent DATAO-D.

CON I-D

: reads state of TZA flag into bit 25. TZA is

cleared by DATAO-D and set shortly thereafter

when the overwritten data is available to be

read by DATAI-D. Between the DATAO-D and the

setting of TZA no DATAO should be given to

the synthesizer.

comes in Right-adjusted

bits 16-35 (no M.A.)

```

how does at the Right ady?

#### CENERATORS

## Parameters

Associated with each generator are the following quantities:

- 60 (20 bits) alpha -- oscillator frequency sweep rate

- GJ (28 bits) omega -- oscillator frequency

- GK (20 bits) theta -- oscillator angle

- GN (11 bits) number of cosines to be summed

- CM (4 bits) binary scale of cosine or sum of cosines

- GP (20 bits) delta -- decay rate

- GQ (24 bits) phi -- decay exponent

- GL (12 bits) asymptote

- GSUM (6 bits) sum memory address into which output is added

- GFM (7 bits) sum memory address from which frequency modulation data is taken

GFM = QAAAAAA

Q: 0 generator-last-pass quadrant

1 modifier-last-pass quadrant

AAAAAA: sum address within quadrant

GMODE (10 bits) generator mode GMODE = RRRREESSSS

## Run Mode

| RRRR: 0000 | inactive                          |      | env. run? add                   |     |  |  |  |

|------------|-----------------------------------|------|---------------------------------|-----|--|--|--|

|            |                                   | no   | no                              | no  |  |  |  |

| 0001       | pause                             | no   | no                              | no  |  |  |  |

| 1111       | running A                         | yes  | yes, sticky                     | yes |  |  |  |

| 1110       | running B                         | yes  | yes, free;                      | yes |  |  |  |

|            | ,                                 |      | triggers subseq.                |     |  |  |  |

| 1001       | wait                              | yes  | no                              | no  |  |  |  |

| 1101       | running C                         | yes  | yes, free;<br>stops and         | yes |  |  |  |

|            | :                                 |      | triggers subseq.<br>on overflow |     |  |  |  |

| 0111       | read data from compute:           | r no | yes                             | yes |  |  |  |

| 0011       | write data to computer            | no   | no                              | no  |  |  |  |

| 0010       | write data to DAC (address in GO) | no   | no                              | no  |  |  |  |

The envelope side of the generator can be sticky, which means that rather than overflow it will stay at the last value it attained before it would have overflowed; or it can be free, in which case it wraps around.

Transitions between run modes can be accomplished in various

- 1) A command can output a new GMODE.

- 2) A MISC command can specify "clear all pause bits", which will cause any generator in run mode 0001 to change to mode 1111.

- 3) A MISC command can specify "clear all wait bits", which will cause any generator in run mode 1001 to change to mode 1111.

- 4) If the envelope side of a generator in run mode 1101 overflows, that generator goes to run mode 1001.

- 5) A generator in run mode 1001 will go to run mode 1101 if on the same pass the preceding generator (the one whose generator number is one less) caused a trigger (was in run mode 1110 or 1101 and envelope overflowed).

#### Envelope Mode

ways.

```

EE: 00 (L + Q)

01 \ge L - Q

10 + L + 2**(-Q)

11 + 1 = 2**(-Q)

```

### Oscillator Mode

```

SSSS: 0000 sum of cosines 0001 sawtooth 0010 square 0011 pulse train sin (K) 1100 sin (J + fm)

```

Calculations performed for a generator, governed by its mode, proceed as detailed below.

- 1) The word in sum memory addressed by GFM is read (20 bits); the sum is formed of it and the high-order 20 bits of GJ (call the result Temp0).

- 2) If the oscillator side is running, GO, right-adjusted with sign extended, is added into GJ.

- 3) If the oscillator mode is 1100, Temp0 is taken; otherwise CK. Call the 20-bit result Temp1E, and its high-order 12 bits Temp1.

- 4) If the oscillator side is running, Temp0 is added into GK.

- 5) If the run mode is 0011, the word in sum memory addressed by GFM is sent to the CPU as write data; if the run mode is 0010, it is sent to the DAC addressed by the low-order 4 bits of GO.

- 6) In oscillator modes other than 0100 and 1100, Templ is multiplied by CN. Call the low-order 12 bits of the product, with two bits equal to 01 appended to the right, the 14-bit result Temp2. In oscillator modes 0100 and 1100, Temp2 is the high-order 13 bits of Temp1E, with a bit equal to 1 appended to the right.

- 7) If the oscillator mode is 0100 or 1100, pi/2 is taken (the binary number 010...0); otherwise Temp1. Call the result Temp3.

- 8) In floating point, the product csc (Temp3) \* sin (Temp2) is formed; then converted to fixed point with a scale factor of 2\*\*(-CM); then 2\*\*(-CM) is subtracted if CM is nonzero. Call the result (12 bits) Temp4.

- 9) The result of the oscillator side (12 bits, call it Temp5) is then determined according to the oscillator mode.

SSSS: 0000 Temp4

0001 Temp1

0010 -1/2 (on a scale from -1 to +1) if Temp1 is negative, else +1/2

0011 +1/2 if overflow occurred in step 1) or 4) above; else 0.

0100 Temp4

1100 Temp4

- 10) The high-order 12 bits of GQ are taken (call this Temp6).

- 11) If the envelope side is running, GP right-adjusted, sign extended, is added into GQ (overflow dealt with according to the run mode). (The overflow condition is GQ changing sign such that the high-order bit of the resultant GQ equals the sign bit of GP.)

- 12) If the envelope mode is 10 or 11, 2\*\*(-Temp6) is looked up; otherwise Temp6 is taken. Call the resulting 12 bits Temp7. Scaling is such that if Temp6 is 0, then 2\*\*(-Temp6) is 111 111 111 binary; if Temp6 is 000 100 000 000 binary, then 2\*\*(-Temp6) is 011 111 111 111.

- 13) If the envelope mode is 00 or 10, Temp7 is added to GL; else it is subtracted from GL. This creates Temp8, the result of the envelope side.

- 14) Temp5 is multiplied by Temp8. If the run mode specifies adding into sum memory, the high-order 18 bits of the rounded product, right-adjusted with sign extended, are added into the sum memory location designated by CSUM; except that in run mode 0111, the product is added to read data from the CPU and the sum replaces the contents of the sum memory location addressed.

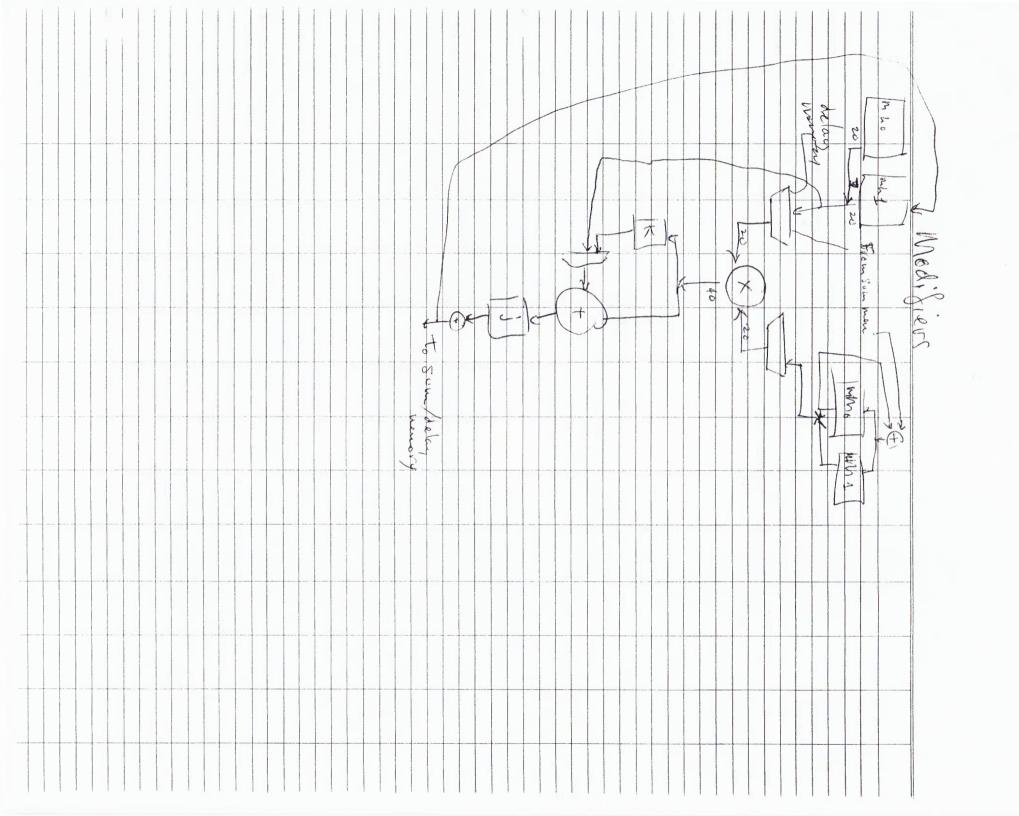

#### MODIFIERS

## Parameters

Each modifier has the following numeric parameters.

- MO (30 bits) coefficient

- M1 (30 bits) other coefficient

- L0 (20 bits) running term

- L1 (20 bits) other running term

- MIN (8 bits) address in sum memory where modifier reads "A" data

- MRM (8 bits) address in sum memory where modifier reads "B" data MIN, MRM = QQAAAAAA

- QQ: 00 generator-last-pass quadrant

- 01 modifier-last-pass quadrant

- 10 modifier-this-pass quadrant

- 11 (reserved)

- AAAAAA: sum address within quadrant

- MSUM (7 bits) result address in sum memory

MSUM = RAAAAAA

- R: 0 add to sum

- 1 replace sum

AAAAAA: sum address in modifier-this-pass quadrant

```

MMODE (9 bits) modifier mode

MMODE = MMMMMAABB

AA: scale of first multiplication

00: x1/4

BB: scale of second multiplication

00: x 1

01: x 2

10:11

10: x 4

111/2

11: x 8

A multiplication involving parameter M1 will be the first

multiplication; one involving MO will be the second.

MMMMM: function

00000: inactive

00010:

uniform noise

00011:

triggered uniform noise

00100: latch

00110:

threshold

00111:

invoke delay unit

01000:

two poles

01001:

two poles, MO variable

01011: two poles, MI variable

01100: two zeros

01101: two zeros, MO variable

01111:

two zeros, MI variable

10000:

integer mixing

10001:

one pole

```

10100:

10110:

11000:

11001:

11010:

11011:

11100:

11101:

mixing

one zero

minimum

maximum

signum

others: (reserved)

amplitude modulation

zero-crossing pulser

four-quadrant multiplication

# Processing

Computations performed by a modifier depend entirely on its mode. In the descriptions below, A is the 20-bit sum memory word addressed by MIN; B is the word addressed by MRM; when MO or MI is used, its high-order 20 bits are taken, but when a quantity is added to MO or MI it is added right-justified, with sign extended; S is the result that is added into the sum memory location addressed by MSUM. Multiplications are 20 bits x 20 bits, signed, and the product (unless otherwise noted) is the high-order 20 bits, rounded.

# MMMMM

- 00000: inactive. S := 0

- 10000: integer mixing. S := A\*M0 + B\*M1 (integer multiply, low-order 20 bits of product used; overflow ignored)

- 10100: mixing. S := A\*M0 + B\*M1

- 00100: latch (sample and hold). S := L1; If B\*M1 is not 0, L1 := A

- 11100: signum. If A\*M0 is less than B\*M1, then S := -1 (integer); if A\*M0 equals B\*M1, then S := 0; if A\*M0 is greater than B\*M1, then S := 1 (integer)

- 11101: zero-crossing pulser. Temp0 := B\*M0; Temp1 := L1\*M1; if Temp1 is not 0 and either Temp0 is 0 or Temp0\*Temp1 is negative then S := -epsilon, else S := 0; L1 := Temp0 (The term -epsilon is a binary number with all bits set.)

- 11010: minimum. S := min (A\*M0, B\*M1)

- 11011: maximum. S := max (A\*M0, B\*M1)

- 11000: amplitude modulation. S := L1\*M1; L1 := A \* ((B+1)/2)

(The term ((B+1)2) interprets B as a signed two's-complement fraction ranging in value from -1 to +1-epsilon.)

- 11001: four-quadrant multiplication. S := L1\*M1; L1 := A\*B

- 10001: one pole. S := L1\*M1 + B\*L0; L1 := S

- 10110: one zero. S := L1\*M1 + L0\*M0; L0 := L1; L1 := A

- 01000: two poles. S := L1\*M1 + L0\*M0 + A; L0 := L1; L1 := S

- 01001: two poles, M0 variable. S := L1\*M1 + L0\*M0 + A; L0 := L1; L1 := S; M0 := M0 + B

- 01011: two poles, M1 variable. S := L1\*M1 + L0\*M0 + A;L0 := L1; L1 := S; M1 := M1 + B

- 01100: two zeros. S := L1\*M1 + L0\*M0 + A; L0 := L1; L1 := A

- 01101: two zeros, M0 variable. S := L1\*M1 + L0\*M0 + A;L0 := L1; L1 := A; M0 := M0 + B

- 01111: two zeros, Mi variable. S := L1\*M1 + L0\*M0 + A; L0 := L1; L1 := A: M1 := M1 + B

- 00010: uniform noise. S := L0 + L1\*M0 (integer multiply, low-order 20 bits of product used; overflow ignored); L1 := S

- 00011: triggered uniform noise. S := L0 + L1\*M0 (integer multiply, low-order 20 bits of product used; overflow ignored); if (B\*Mi) is not 0, L1 := S

- 00110: threshold. If A\*M0 + L0 is less than 0, then S := 0; if A\*M0 + L0 is equal to or greater than 0, then S := B\*M1

## Timing Considerations

The following relationships apply to references to the modifier-this-pass quadrant of sum memory.

- Modifier number M writes into sum memory (read-add-write or replace) on tick number 2\*M + 7.

- 2) Modifier number M reads word B on tick number 2\*M.

- 3) Modifier number M reads word A on tick number 2\*M in the following modes: integer mixing; mixing; signum; minimum; maximum; amplitude modulation; four-quadrant multiplication; threshold.

- 4) Modifier number M reads word A on tick number 2\*M + 6 in the following modes: latch; one zero; two poles, two zeros (all six modes); invoke delay unit.

muttipl?

Los this men that on an area of the sound of the most the sound of the men the sound of the men that the men

#### DELAY UNITS

A common pool of addressable memory, which may comprise up to 65,536 20-bit words, is available for use by the delay units. By programming, each active delay unit is assigned its own contiguous area of the memory.

# Quantities

Each delay unit has the following numeric parameters.

P mode (4 bits). The mode is interpreted as follows: mode: 0000 inactive

1000 delay line 1010 table look-up

1011 table look-up, argument rounded

others: (reserved)

- Z unit length (16 bits) or binary scale factor (4 bits).

In delay line mode, Z gives the total number of locations in the delay line, i.e. the number of samples of delay the unit comprises. In table look-up modes, the low-order four bits of Z specify the number of binary places that the argument is shifted to the right before it is used to address the memory.

- Y index (16 bits). In delay line mode, this is the running index on the memory area for the unit.

- X base address (16 bits). The base address is the lowest-numbered sum memory location used by this unit.

## Processing

In inactive mode, delay memory is not modified and the unit returns indeterminate results. Delay units not accommodated due to the number of ticks in a pass act as if in the inactive mode.

In delay line mode, a 20-bit data word is received from the modifier that calls for the delay unit, and another 20-bit word is sent to it. The word received is put into the next slot in the delay line. It will be retrieved and sent back to the modifier Z+3 passes later.

In table look-up mode, the 20-bit data word received from the modifier is shifted to the right Z bits, bringing in zeros, and the right 16 bits of the result are used to address the memory area assigned to the unit. The 20-bit word in the addressed memory location is returned to the modifier three passes later.

#### COMMANDS

All commands have 32 bits. Generally the left 20 bits are data, the next 4 or 5 bits identify the kind of parameter, and the last 8 or 7 bits address the generator or modifier affected. If more than one data field is packed in the 20 bits, disable bits will be provided to facilitate loading a subset of the fields. In a few cases, a bit is also provided in the data area to clear (put to zero) a related parameter in the same generator or modifier.

| :  |          |               |              | data                                     | :                   |      |                | V:           | (7)         | mod       | #  | :     |      |    |

|----|----------|---------------|--------------|------------------------------------------|---------------------|------|----------------|--------------|-------------|-----------|----|-------|------|----|

|    | vv:      | 0             | 1 M1<br>0 M0 | right-a<br>right-a<br>left-ad<br>left-ad | djusted,<br>justed, | l, s | ign e<br>w bit | xter<br>s fr | nded<br>rom | l<br>left |    |       |      |    |

| :  |          |               |              | data                                     |                     |      |                | N:           | (7)         | mod       | #  | :     |      |    |

|    | N:       | <b>0</b><br>1 | L0<br>L1     |                                          |                     |      |                |              |             |           |    |       |      |    |

| :  |          |               | (20)         | data                                     |                     | 0 0  | 1 : E :        | (            | (8)         | gen       | #  | :     |      |    |

|    | E:       | 0             |              | ght-adju<br>ft-adjus                     |                     |      |                |              |             | t of      | DX | ; cle | ar D | K  |

| :  |          |               | (20)         | data                                     |                     | 0 1  | 1 0:           |              | (8)         | gen       | #  | :     |      |    |

| :  |          |               |              | data                                     |                     |      |                |              |             |           |    | :     |      |    |

|    | E:       | 0             |              | ght-adju<br>ft-adjus                     |                     |      |                |              |             | ft of     | DX | i cle | ar D | X. |

| :1 | N:M:x    | ×             | x: (1        | 1) GN : (                                | 4) GM               | :0 1 | 1 1:           |              | (8)         | gen       | #  | :     |      |    |

|    | N:<br>M: | i             | lf 1,        | disable<br>disable                       | loading             | g GN |                |              |             |           |    |       |      |    |

```

GL, :L:S: (12) GL : (6) GSUM : 1 0 0 0: (8) gen # :

GSUM----

L: if 1, disable loading CL

S: if 1, disable loading GSUM

CK :

(20) data :1 0 0 1: (8) gen # :

:M:S:C:2:(9) MMODE :(7) MSUM:1 1 1 1 0: (7) mod # :

MMMMM desable loading AABB

MMODE.

MSUM

M: if 1, disable loading MMODE

S: if 1, disable loading MSUM

C: if 1, clear L0

:R:I:C:x: (8) MRM: (8) MIN:11111: (7) mod #:

MRM.

MIN

R: if 1, disable loading MRM

I: if 1, disable loading MIN

C: 'if 1, clear L1

:M:F:C: (10) GMODE:(7) GFM:1010: (8) gen #:

CMODE.

GFM

M: if 1, disable loading CMODE

F: if 1, disable loading GFM

C: if 1, clear GK

:1 0 1 1:

:0 0 0 0 0:x x:R R:W:P:S:

MISC----

RR: 00 no effect

01 load DX from data

load TTL buffer A from left 16 bits of data

load TIL buffer B from left 16 bits of data;

set analog output filters from right 4 bits of data:

OOxx Mode O

Odnn Mode 1, frequency fo, f1, f2, or f3 according

Ò

to nn

1xxx no change,

W: if 1, clear all wait bits

P: if 1, clear all pause bits

S: if 1, stop

```

```

(20) data

:0 0 0 1 0:x x:T T:x x x:

TIMER

TT: 00 no effect

10 Linger: process no further commands until pass counter

equals data

11 clear pass counter, then Linger as for 10

(generation)

01 set pass counter from data

: xxx xxx xxx x : (10) data :0 0 0 1 1:x x:0:Q:x x x:

* TICKS

Q: 0 designate highest-numbered processing tick per pass (takes I mode tix There you say)

(should not exceed 255)

1 designate highest-numbered tick, (processing plus

(take 2 more Tix than you my)

update) per pass

recale mode 7

:(4)data:0 0 0 0 1:U U:(5)unit #:

DLY X, Y, Z

UU: 00 X

16 bits base address; clear Y

.01 Y

16 bits index

10 Z,P 16 bits delay unit size, or scale (low 4 bits of

16); 4 bits mode

11 (unused)

```

generator

The signal path for one analog output involves the following sections:

Channel selection logic (addressing)

Digital hold register

Digital to analog converter

Sample-and-hold

Program-controlled filter

Buffer amplifier.

Each section is specified at 25 degrees C as follows.

Channel selection logic: 4 bits (1 of 16)

Digital hold register: 14 bits

Digital to analog converter: 14 bits

Linearity: 0.005%

Sample-and-hold: full power bandwidth 40 kHz

Filter: two modes

Mode 0: 1-pole RC at 200 kHz

Mode 1: 6-pole Butterworth, 4 programmable frequencies subject to the relationships f0=A, f1=A+B, f2=A+C, f3=A+B+C; full power bandwidth 18.5 kHz max.

Buffer amplifier: output +/- 10 V max., unbalanced

Output current: 4 mA max.

Short circuit protection: to ground only

Full power bandwidth: 13 kHz for 20 V swing; greater in

proportion for lower voltages

Output source impedance: 100 ohms

Output connector: BNC jack

The following are overall figures with Mode 0 filtering:

Gain error: 2.5%

Offset error: 20 mV

Noise at sampling rate and its harmonics: 1 mV max. (RMS)

Other noise 10 Hz to 50 kHz: 1 mV max. (RMS)